採用定制 FPGA 主機板導入物聯網適用的軟體定義無線電

物聯網涵蓋非常廣泛的應用範圍,通常單一設計就需要超過一個無線介面,佔用更多空間也花費更多電力和成本。內行的物聯網網路設計師必須具備靈活彈性,才能支援多種不斷演變的標準,而使用軟體定義無線電 (SDR) 技術,就是獲得靈活彈性的另一種方法。SDR 技術並不是新概念;但是改寫 SDR 來解決物聯網面臨的兩難局面卻是新做法,所謂的兩難就是要在相同的網路基礎架構上整合多種射頻技術,還要簡化設計、縮短開發週期和降低整體成本。本文介紹一個以定制 FPGA 主機板為基礎的 SDR 設計,這是用來建立多重通訊協定無線數位基頻解決方案的設計。

SDR 提升網路插槽的效能與效率

顧名思義,SDR 技術可以在相同的硬體上支援多種無線電通訊協定。視實作情況而定,它可以同時支援這些通訊協定,且能橫跨非常廣泛(或狹窄)的頻譜範圍。而且,若在基地台一類無線裝置中使用 FPGA 實作時,隨著無線連接通訊協定不斷演變,您甚至可以重新編寫 SDR 平台的程式,讓網路基礎架構在未來繼續適用。VotaryTech 的 SDR 平台 Arria 10AX115U3F4512SG 便是能夠展現 SDR 潛力的好例子(圖 1)。這款 Intel® Arria® 10 FPGA 是支援系統單晶片的網路卡,適用於各式各樣的無線應用,包括全球行動通訊系統 (GSM)、通用封包無線服務 (GPRS)、LTE 網路的寬頻訊號處理、追蹤和遙測。該主機板是前端射頻平台,支援介於 70 MHz 至 6 GHz 之間的無線應用,不過它可以擴大至最高 15 GHz 的頻率。

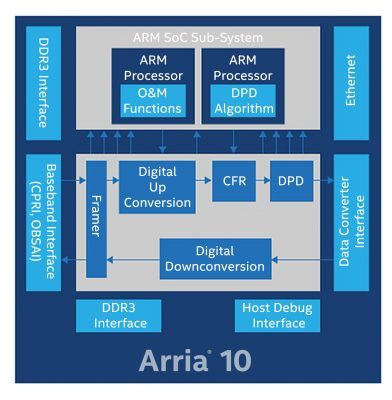

定制的 10AX115U3F4512SG 支援網路應用的所有訊號處理要求,包括各種調變與解調方案。主機板的基頻處理能力涵蓋數位升頻器、數位降頻器以及標準調變器與解調器通訊核心。這樣一來,這個 SDR 平台便能在無線設計中支援傳送及接收訊號。再者,因為採用 10AX115U3F4512SG,所以 Arria 10 FPGA 內部的基頻處理作業可以程式化及微調,如此便能執行諸如 IF 過濾和降頻等工作。

為何在 SDR 中使用 FPGA

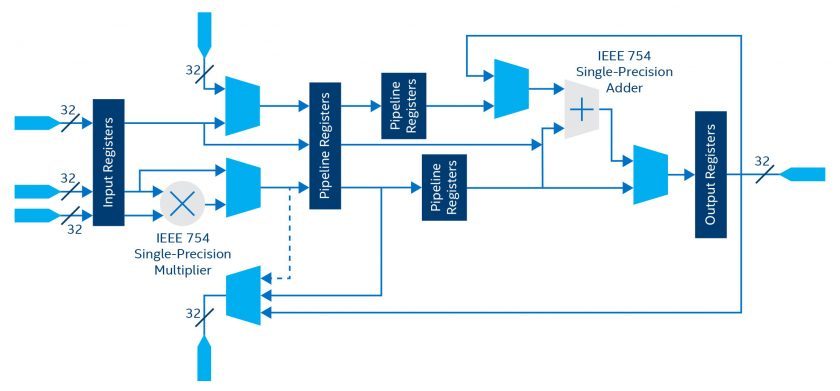

早期採用射頻前端模組的 SDR 設計曾經讓工程師驚艷且展現極大潛力。但是這項技術由於缺乏應用,SDR 設計並未能取得實質的進展,部份原因是這類系統中定制 ASIC 的要求(與成本)。但如今,低風險的系統單晶片正逐漸取代 SDR 平台中使用的傳統 ASIC。例如,採用 20 奈米製程技術建構的中階 FPGA 系統單晶片如 Intel Arria 10,相較於前一代高階 FPGA,其效能提升了 15% 且能耗降低了 60%(圖 2)。該裝置所產生的熱也較少,這也是無線基地台、行動回程傳輸以及遠端射頻轉發器設計的重要考量因素。更重要的,Intel Arria FPGA 系統單晶片提供數種精準度可變的 DSP 區塊和雙核心 Arm Cortex-A9 處理器的選項。Arria 10 FPGA 系統單晶片中的 DSP 區塊提供三種模式:標準精準度定點、高精準度定點和單一精準度浮點(圖 2)。無線系統設計師可藉此為數位升頻和降頻及多取樣率濾波器導入各種不同的演算法。

把這些運算能力與超過 100 萬個 FPGA 邏輯元素 (LE) 和 2,400 Mbps DDR4 SDRAM 記憶體介面結合,便打造出可高度程式化、可調整的平台,能夠接納現有和新進的無線技術(圖 3)。

可合成的 IP 核心也可以整合到 FPGA 架構中,允許無線設備設計師為 FPGA 內的基頻提供類比數位轉換器 (ADC) 輸出和數位類比轉換器 (DAC) 輸入。這搭配上 I/O 和通訊協定控制,就是促使 SDR 型射頻處理與基頻介面之運作更便利的重要角色。可輕鬆取得電路圖並提供 10AX115U3F4512SG 適用的 Gerber 和主機板檔案,簡化了 SDR 功能之整合作業。Arria 10 支援通用公共射頻介面 (CPRI) 規格,使得平台更加適合無線基地台設計。

可程式化的能力已到達物聯網門檻

VotaryTech 原本是為了一項無線數據機應用研發這個 SDR 設計,但是因為硬體可程式化,所以也可以用在諸如遙測和波形產生模擬器一類應用。Arria 10 FPGA 系統單晶片帶來了這樣的靈活彈性,使得 10AX115U3F4512SG 這類主機板非常適合包含各種各樣演變中的技術和應用的物聯網。但是最重要的事,也許是本文已論證小型設計公司如何能運用高配置性的 FPGA 系統單晶片的威力,來提供能應付現有和未來要求的解決方案。